|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Divisore Programmabile di frequenza - 5 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

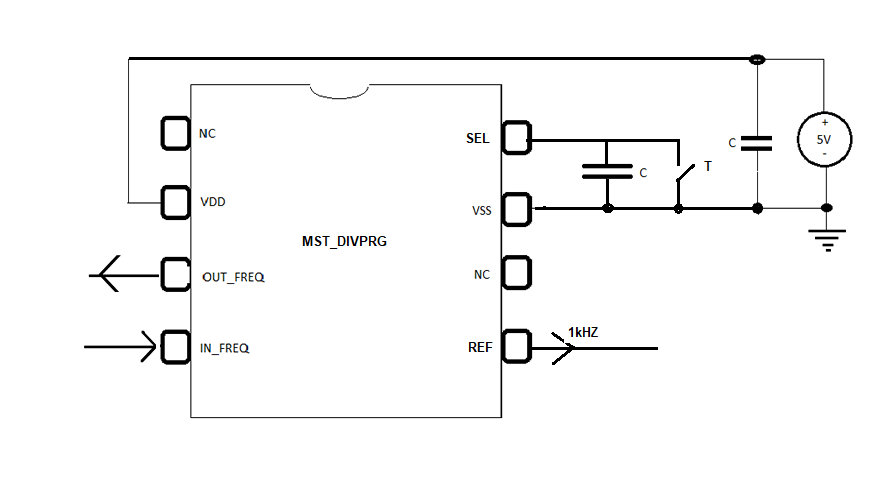

Il chip MST_DIVPRG In

figura il chip MST_DIVPRG

che implementa il divisore programmabile presentato nelle pagine

precedenti. Il chip

e' nel package DIP8.

Di

seguito la descrizione dei pin

Di seguito alcuni parametri elettrici del chip

In figura lo schema applicativo del chip MST_DIVPRG

Il

segnale di ingresso deve essere applicato all' ingresso IN_FREQ mentre

il segnale di uscita e' prelevabile dal pin OUT_FREQ. I valori di divisione sono preimpostati ai valori 100, 200, 500, 1000, e sono selezionabili tramite il pin SEL. Ad ogni fronte di discesa del pin SEL si passa al successivo valore di divisione in maniera circolare. Dal pin REF è prelevabile un segnale di riferimento alla frequenza di 1kHz utilizzabile come segnale di riferimento

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||