|

|

|||

|

SONDA LOGICA CMOS |

|||

|

|||

|

|

|||

|

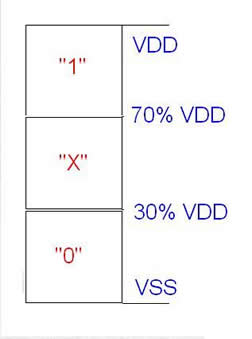

Utile indicatore di stati logici per dispositivi con integrati CMOS. E un rivelatore che può essere utilizzato anche in altre applicazioni. Progetto di una sonda per circuiti CMOS. Coloro che operano con questi integrati ne avranno avvertito la necessità. Quelli, invece, che non possono apprezzare l'utilità del dispositivo, qui presentato e descritto, per non aver mai lavorato con i CMOS, debbono sapere che, prima o poi, potranno trovarsi nelle condizioni di intervenire in qualche apparato, nel quale sono montati questi componenti, e sul quale si debbono effettuare misure e controlli. A costoro, peraltro, prima di descrivere la sonda, dobbiamo ricordare alcuni elementi relativi alle tecnologie moderne CMOS. Nell'iniziare, quindi, un discorso di carattere generale, cominciamo col dire che, oltre alla tecnologia bipolare, con la quale vengono prodotti i circuiti integrati logici, chiamati pure digitali, della serie 74, esiste anche quella MOS complementare, che consente di realizzare, sullo stesso substrato, attraverso un unico processo produttivo, transistor MOS, sia a canale N che a canale P, con caratteristiche elettriche simmetriche. E questi transistor sono realizzati in modo che, in assenza di polarizzazione di gate favorevole, non presentino alcun canale di conduzione tra source e drain, mentre, se polarizzati per la conduzione, il gate forma elettrostaticamente un canale conduttivo tra source e drain, consentendo la conduzione elettrica tra i due elettrodi con una resistenza abbastanza bassa. Ma entriamo maggiormente nei dettagli e consideriamo il atto per cui, dimensionando opportunamente i vari parametri dei transistor, si può far in modo che la tensione di polarizzazione, necessaria per far entrare in conduzione i transistor CMOS, sia la stessa in valore assoluto. Ebbene, sfruttando questo vantaggio e collegando in serie tra di loro due transistor CMOS" uno a canale N e l’altro a canale P, purche il primo abbia la source collegata a massa ed il secondo alla linea positiva dell'alimentazione, qualora ai due gate, collegate assieme, venga applicata una tensione di valore inferiore di un terzo di quella di alimentazione, il canale P entra in conduzione, mentre rimane aperto il canale N. Conseguentemente, il circuito d'uscita si trova allo stato logico "1", chiamato pure "alto", equivalente ad una resistenza di basso valore collegata alla linea positiva dell'alimentazione. Viceversa, se la tensione applicata ai gate supera della misura del 70% quella di alimentazione, le vicende si invertono e l'uscita diviene bassa, ossia occupa lo stato logico "0", equivalente, questa volta, ad una resistenza di basso valore collegata a massa. Tra il 30% ed il 70% del valore della tensione di alimentazione, entrano in conduzione piu o meno lieve i due CMOS e l'uscita raggiunge uno stato intermedio. In tali condizioni il CMOS e’ piu adatto ad applicazioni lineari che non digitali. , quelle che sono state ora descritte, rimangono sintetizzate nello schema riportato in figura 1.

Fig.1 - condizioni in cui si può trovare un circuito CMOS e relative tensioni VARIETÀ DI CMOS Esistono circuiti CMOS, in tecnologia "silicon

gate" in grado di funzionare con tensioni di alimentazione di valori

compresi fra i 3 V e i 16 V, con basse frequenze di commutazione ,fra i

pochi megahertz e i 20 MHz, a seconda dei vari modelli e delle

applicazioni cui sono destinati . Ma esistono pure circuiti CMOS, in

tecnologia "metal gate" che funzionano con tensioni di alimentazione di

valore compreso fra i 2 V e i 7 V con frequenze pari a quelle della

famiglia bipolare 74LS (fra le decine di MHz e gli 80 MHz). Alla prima

famiglia, ora menzionata, appartengono gli integrali della serie 4000,

di cui ci occuperemo in questa sede. Della seconda fanno parte. i

modelli della serie 74HC e quelli, meno diffusi, della serie

74HCT. |

|

||

|

|

|||

|

|

|||

|

|

|||