|

Classificazione dei circuiti logici

Circuiti combinatori e sequenziali

Un circuito è detto "combinatorio" se le sue

uscite sono determinate unicamente dagli ingressi.

Un circuito è detto "sequenziale" se le sue uscite non

dipendono solamente dagli ingressi, ma anche dagli stati precedenti

(dalla storia del circuito); è un circuito dotato di memoria.

I circuiti sequenziali si dividono in sincroni e

asincroni.

I circuiti sequenziali "sincroni" sono caratterizzati

dalla presenza di un segnale di clock; in corrispondenza del fronte

attivo del clock, il sistema passa da uno stato al successivo e le

uscite assumono un nuovo valore.

I circuiti sequenziali "asincroni" sono circuiti

sequenziali il cui funzionamento non si basa su un segnale di clock di

sistema; in essi si passa da uno stato ad un altro solo in seguito al

cambiamento di livello di un segnale di ingresso esterno.

Convenzioni e Definizioni

Clock

In

molti circuiti digitali l’ordine temporale con cui si verificano gli

eventi è una caratteristica significativa. Per definire e scandire il

tempo, nei circuiti digitali si deve introdurre il segnale di clock (o

di temporizzazione).

Il clock è un segnale binario, con andamento periodico nel tempo.

Il segnale di clock è una successione

di impulsi a larghezza costante e due impulsi di clock consecutivi

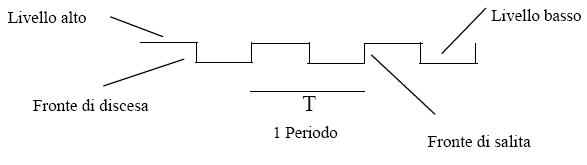

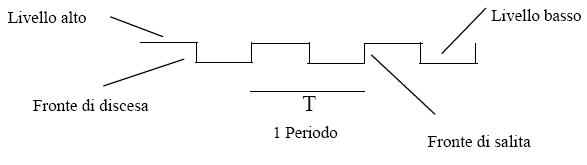

stanno a una distanza costante. Dalla figura 1 si possono evincere i

parametri caratteristici di un segnale di clock:

Fig. 1 esempio di segnale di clock e i relativi parametri

Sincronizzazione

Vi sono

in realtà due modi per sincronizzare un circuito con il clock:

-

sincronizzazione

sul livello: nell’intervallo alto del clock gli ingressi del

circuito sincronizzato sono efficaci (fenomeno della trasparenza);

nell’intervallo basso lo stato del circuito è congelato

-

sincronizzazione

sul fronte : gli ingressi al circuito sono efficaci solo

all’istante del fronte di salita del clock, ma in entrambi gli

intervalli alto e basso del clock lo stato del circuito è congelato! il

fenomeno di trasparenza non esiste!

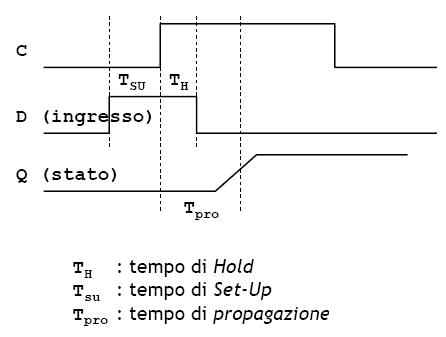

Tempo

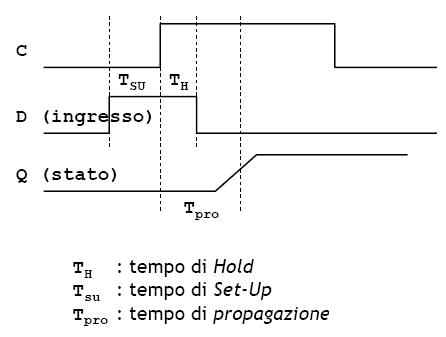

di setup (t_su)

Intervallo

di tempo prima della commutazione del clock durante il quale

l’ingresso del circuito deve avere un valore stabile e costante.

Tempo

di hold (th)

Intervallo

di tempo dopo la commutazione del clock durante il quale

l’ingresso deve mantenersi stabile e costante.

Tempo

di ritardo ( tpro)

Intervallo

di tempo che trascorre dalla commutazione del clock all’istante in cui

l’uscita assume un valore logico definito e stabile.

In figura 2 sono descritti graficamente le definizioni di t_su, th

e di tpro

Fig.2 Descrizione grafica di Tsu, TH e Tproi

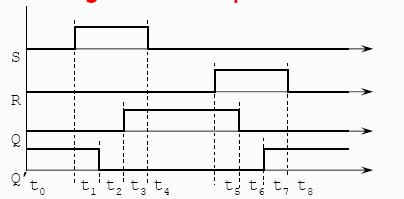

Equazione

di funzionamento

Espressione

logica del funzionamento del circuito ricavata dalla tabella

delle transizioni esempio di

equazione .Q* = S + R’Q Con vincolo S=R≠1

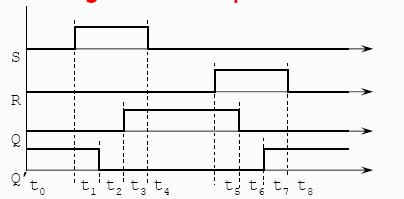

Diagramma

Temporale

Il

diagramma temporale esprime graficamente l'andamento dei segnali di

ingresso e di uscita lungo l'asse dei tempi. In figura 3 e' riportato

un esempio di diagramma temporale di un circuito sequenziale.

Fig.3: esempio di diagramma temporale di un circuito

sequenziale

|