|

|

||

SPI

(Serial Peripheral Interface)

|

||

|

||

|

|

||

|

Introduzione

all'interfaccia SPI L’interfaccia

SPI acronimo di (Serial peripheral

interface) è una delle interfacce più utilizzate nei

microcontrollori e usata per mettere in comunicazione circuiti periferici come sensori, ADC, DAC, registri a scorrimento, SRAM e

altri. Questo

tutorial fornisce una breve descrizione dell'interfaccia SPI

a 4 fili. Un tutorial sulla interfaccia SPI nei microcontrollori

PIC e come configurala e' presente in questo sito a questo link SPI_PIC

La SPI

è un'interfaccia di tipo master-slave sincrona, full duplex. I dati

scambiati tra

il master e lo slave sono sincronizzati sul fronte di salita o di

discesa del

clock (linea SCK). Sia il master che lo slave possono trasmettere dati

allo

stesso tempo. L'interfaccia SPI può essere a 3 o 4

fili.

I dispositivi SPI a 4 fili utilizzano 4 linee di segnali:

La

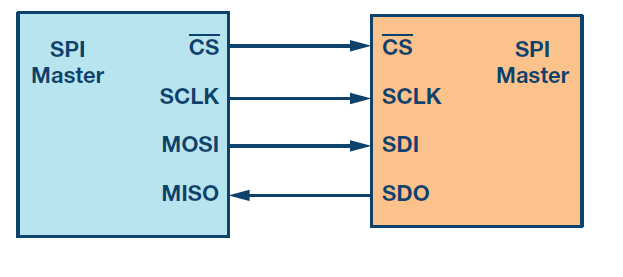

figura 1 mostra una tipica connessione SPI tra master e slave a 4 fili  Figura

1. Configurazione SPI a 4 fili . Il segnale di clock SCLK è generato dal master. I dati scambiati tra il master e lo slave sono sincronizzati sui fronti di questo questo segnale. I dispositivi SPI supportano un clock molto più alto in frequenza ( 40MHz) rispetto alle frequenze delle interfacce I2C ( 3.4MHz versione High Speed Mode). Le interfacce SPI possono avere solo un master e possono avere uno o più slave. Il

segnale di selezione CS (Chip

select)

e’ utilizzato dal master per selezionare lo

slave. Questo è

normalmente un segnale attivo basso e viene tirato in alto per

scollegare lo

slave dal bus SPI. Quando vengono utilizzati più slave, il master

gestisce il CS per ogni slave presente nel bus. Le

linee MOSI e MISO sono le linee dati. La linea MOSI

(Master Output Slave

Input) trasmette i dati dal

master verso lo

slave mentre la linea MISO (Master

Input Slave Output) trasmette

i dati dallo slave verso il master. |

||

|

|